2023/07/02 Misskeyリンクの追加(内容に変更ありません)

2023/02/11 アクセスカウンタ・アクセス解析タグ入れ替え(内容に変更ありません)

2021/03/25 VRAMボードについての加筆・動画追加

2021/03/11 HTMLタグ修正(内容に変更ありません)

2023/02/11 アクセスカウンタ・アクセス解析タグ入れ替え(内容に変更ありません)

2021/03/25 VRAMボードについての加筆・動画追加

2021/03/11 HTMLタグ修正(内容に変更ありません)

目次

1. 概要2. パーツ

3. 回路

4. 製作

5. 実験

6. あとがき

7. 参考にさせていただいたサイト・情報

1. 概要

「ロジックICで作るVGA信号生成回路」(以下、VGA信号生成回路)を製作してから、5年。同期信号を出すだけの機能しかない状態のまま放置していました。

さすがにこれ以上放っておくと、エターになってしまいそうなので、マルチプレクサの塊によるバス調停回路を持った、VRAM回路を製作しました。

それに伴い、製作済みのVGA信号生成回路にも外部接続のための改造を施しました。

さすがにこれ以上放っておくと、エターになってしまいそうなので、マルチプレクサの塊によるバス調停回路を持った、VRAM回路を製作しました。

それに伴い、製作済みのVGA信号生成回路にも外部接続のための改造を施しました。

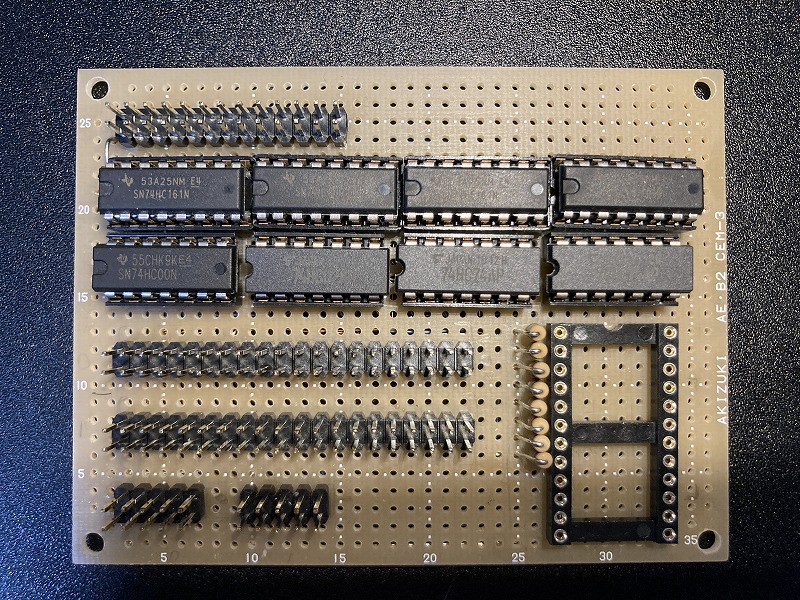

2. パーツ

- ユニバーサル基板(72x95mm) x2

- ICソケット(14pin x4, 16pin x9, 20pin x1, 24pin x1, 28pin x1)

- ピンヘッダ(たくさん(今回も数えてません^^;))

- 0.1uF 積層セラミックコンデンサ x15(パスコン)

- 抵抗 10kΩ x8

- 集合抵抗 10kΩ8素子 x1

- 74HC00 x1

- 74HC02 x1

- 74HC74 x2

- 74HC153 x1

- 74HC157 x4

- 74HC161 x4

- 74HC244 x1

- SRM2B256SLMX55 x1(256kbits 32KiB SRAM 55ns)

- IDCリボンケーブル(10pin x2 26pin x1 40pin x1)

- ミニD-Sub15pinコネクタ(メス) x1

- AE-FT245R(FTDI FT245R)

- Arduino UNO(互換品)

(以下、2021/03/25追記)

2枚目のVRAMボードを作る際は、74HC157, 74HC244, SRM2B256SLMX55がそれぞれ2倍必要になります。

(追記終)

今回も「ワイヤラッピング」を用いて配線した基板があるため、ピンヘッダを大量に使っています。

DIPサイズの74シリーズは次第に入手困難になってきています。今回は、VGA信号生成回路を製作した頃に入手していたICで製作していますが、そろそろ表面実装サイズへの移行が必要になるかもしれません。

(2021/03/25追記 SOPでスレーブVRAMボードを製作しました。)

実験の項で書きますが、VRAMへのデータの書き込みには、FT245RLとArduino UNO(ATmega328P)による2通りを試しています。

2枚目のVRAMボードを作る際は、74HC157, 74HC244, SRM2B256SLMX55がそれぞれ2倍必要になります。

(追記終)

今回も「ワイヤラッピング」を用いて配線した基板があるため、ピンヘッダを大量に使っています。

DIPサイズの74シリーズは次第に入手困難になってきています。今回は、VGA信号生成回路を製作した頃に入手していたICで製作していますが、そろそろ表面実装サイズへの移行が必要になるかもしれません。

(2021/03/25追記 SOPでスレーブVRAMボードを製作しました。)

実験の項で書きますが、VRAMへのデータの書き込みには、FT245RLとArduino UNO(ATmega328P)による2通りを試しています。

3. 回路

SRAMおよびバス調停回路(以下、VRAMボード)と、VRAM書き込み回路(以下、VRAMコントローラ)を1枚の基板に詰め込むと繁雑になるため、2枚の基板に分けました。

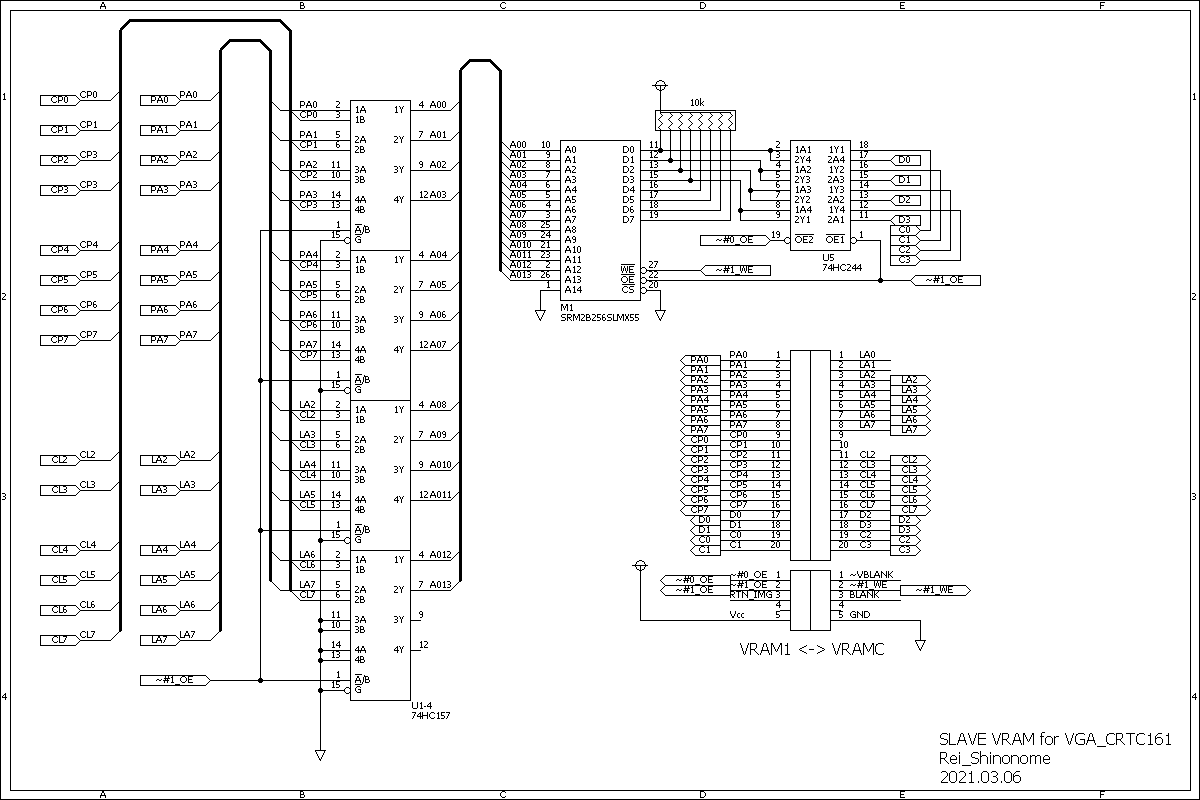

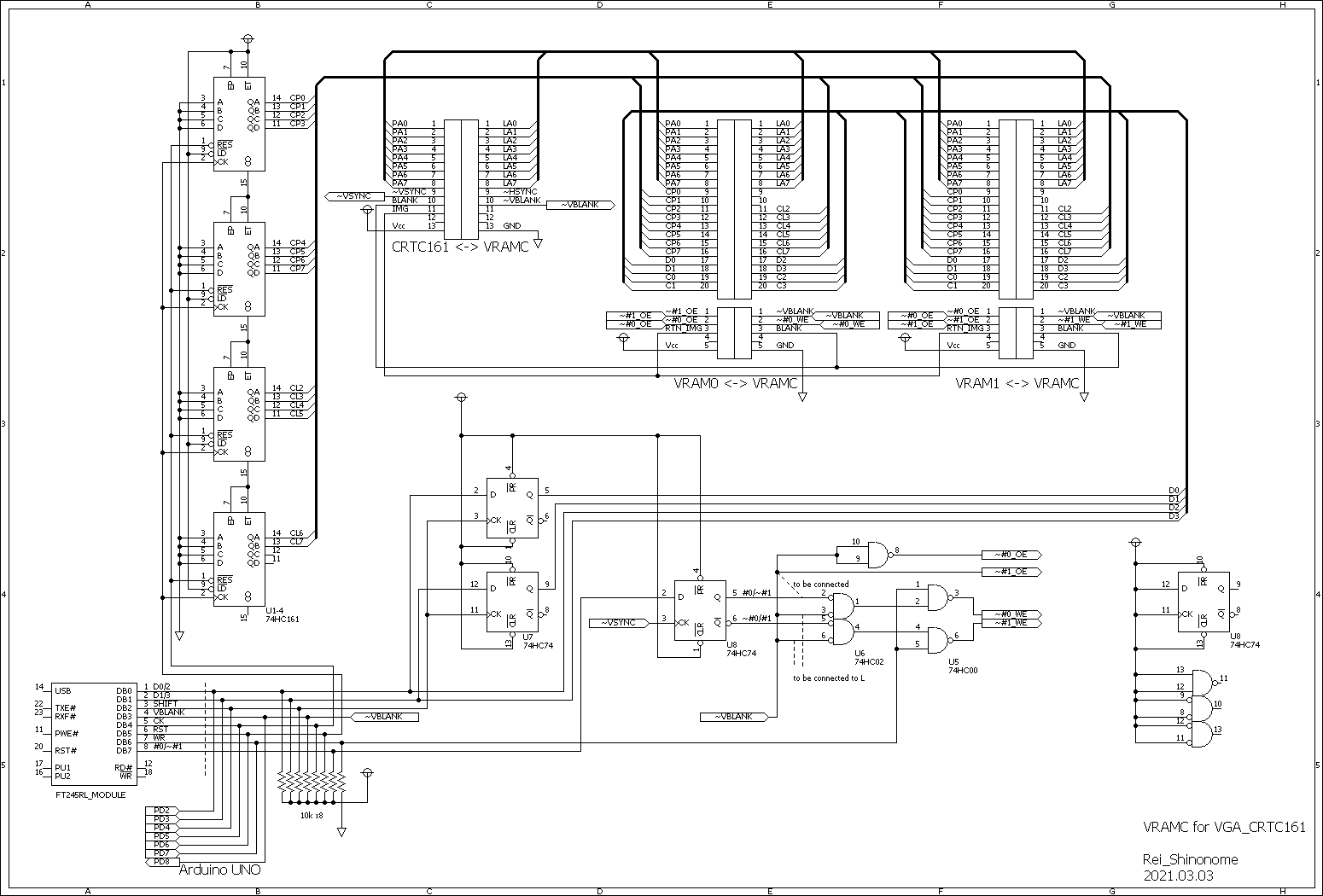

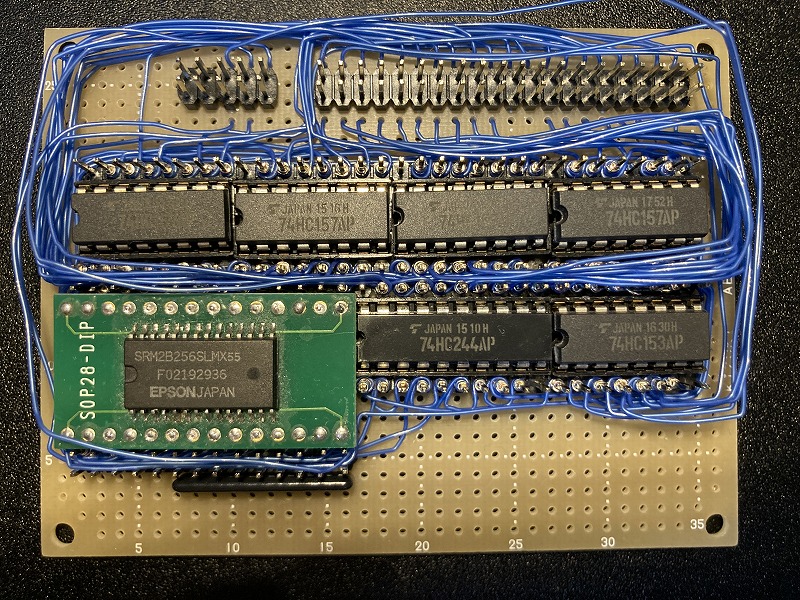

まずは、VRAMボード(2021/03/25追記 マスターVRAM(フレームバッファ)ボード)の回路図です。

VRAMは、垂直方向に4ピクセル分(640x480のスクリーン上では8ピクセル分)を1つのRAMアドレスに格納しています。下位4bitのみ使用していて、上位4bitは使用していません。

RAM領域がもったいないですが、後述するようにホストからのデータ転送に使用するポートが少ないためこのようになってしまいました。

VGA信号生成回路からの画面表示用のVRAMアドレスと、VRAMコントローラからの書き込み用のVRAMアドレスを74HC157で切り替えています。

SRAMのデータバスは、画面表示時と書き込み時で入出力の方向が変わるため、74HC244を用いて方向の制御をしています。

前述の通り4ピクセル分が1つのアドレス内に格納されているため、74HC153に垂直アドレス(ラインアドレス)の下位2bitのアドレスを与えて、各ラインのピクセルデータを分離しています。

74HC153から出力される各水平・垂直方向のアドレスに対応するデータは、VRAMコントローラを経由してVGA信号生成回路まで戻り、その基板からミニD-Subコネクタを通してディスプレイに与えられます。

(2021/03/25 追記)

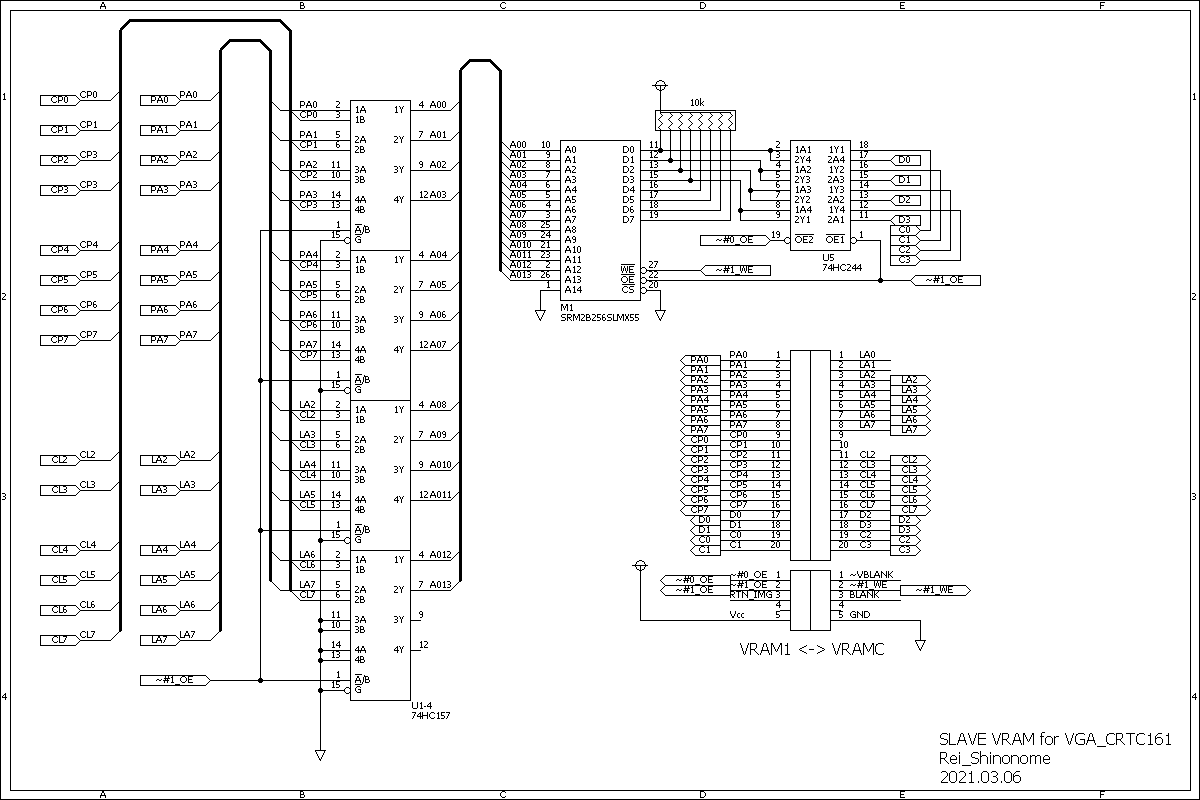

スレーブVRAM(フレームバッファ)ボードの回路図です。

マスターVRAMボードとの違いは、74HC153の有無、OE/WE端子の配置、LA0/LA1端子の有無のみです。

スレーブVRAMボードから出力されたVRAMデータはC0-3端子を通してマスターVRAMボードの74HC153に送られます。マルチプレクサの節約策です。

トレードオフとして、スレーブVRAMボードは単独で画像を出力することはできなくなっています。

(追記終)

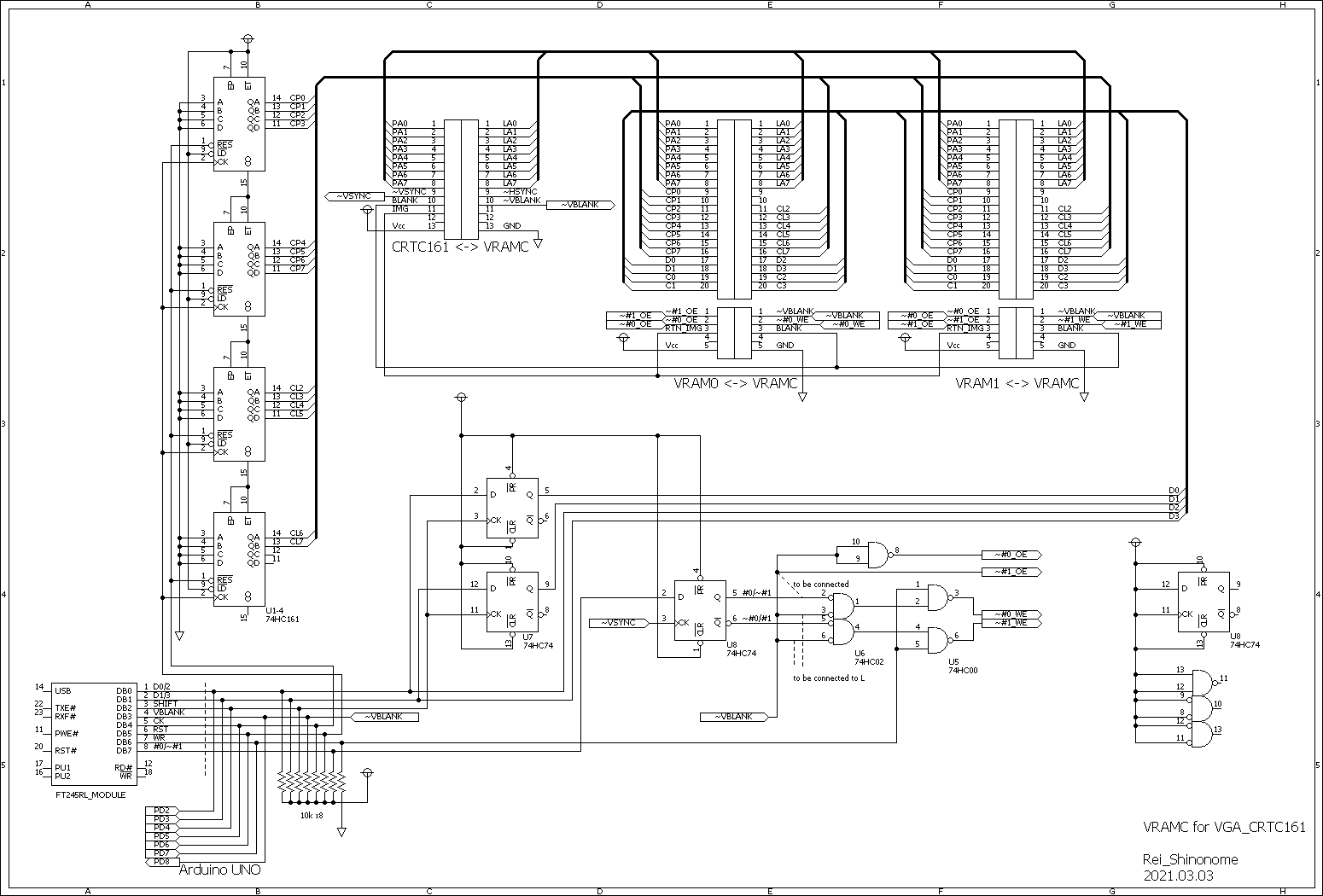

次に、VRAMコントローラ(2021/03/25 追記 VRAMコントローラ/インターフェース)の回路図です。

書き込みアドレスは74HC161を使って、書き込みホスト(FT245R or Arduino)からのクロックで0番地からシーケンシャルに生成します。

FT245Rには汎用ポートが8bitしかないため、コントロールにつかう端子を考えると、8bitのデータを一気に転送することは不可能です。

シフトレジスタを使うことで、クロックとデータの2bitで任意の長さのデータを転送することはできますが、その分オーバーヘッドが生じます。

この点を考慮して、RAMの各番地の8bitの領域をすべて使うことをせず、半分の4bitを使うこととしました。74HC74をシフトレジスタとして使用して、2bitずつ送信します。

VRAMへの書き込みは、垂直ブランキング期間のみ行うため、書き込みホストへは1bitの入力端子を必要とします。

もし、垂直ブランキング期間以外で書き込むと、/WRが/OEに優先されるために、書き込みタイミングでデータバスが奪われ、画面が乱れる原因となります。

表示用アドレスと書き込みアドレスおよびデータはそのまま40pinのコネクタでVRAMに送られます。電源や出力・書き込み信号は別の10pinのコネクタで接続しています。

また、この回路図を見て分かるとおり、VRAMは2段積みが可能な回路になっています。

つまり、片方のVRAM(表示VRAM)の内容の表示中に、もう一方のVRAM(編集VRAM)を書き換えて、表示VRAMと編集VRAMを交代させることができます。

こうすることで、垂直ブランキング期間に関係なくVRAMの内容を書き換えることができ、高速な画面書き換えが可能になります。

そのために、表示VRAMと編集VRAMを指示する信号(回路図中の#0/~#1)も書き込みホストから与えます。

画面表示中にVRAMを交代させると画面が乱れるため、垂直同期のタイミングで交代させられるよう、VRAM指示信号は74HC74で受けています。

ただし、今回は、VRAMボードを1個しか製作していないため、このVRAM交代回路は機能していません。

この回路図上は垂直ブランキング期間以外でVRAMの出力を許可するのみになっています。

VRAMボードを2段積みするときは、U5の9,10番ピンと~#1_OEにはU8の74HC74の出力Qが接続されます。また、~VBLANKが74HC02に入力されている部分はLに固定します。

VRAMボード1枚と2枚いずれにも対応できるよう、ここはスイッチで切り替えられるように予定します。

また、40pinコネクタ内のC0-3は、VRAMボード間のデータ出力の通信線です。VRAMボード2段積みの際に、どちらかの一方のVRAMボードの74HC244の出力を選択し、C0-3の通信線に乗せ、74HC153の入力に与えます。

(2021/03/25 追記 上記打消線も含む)

回路変更が生じています。

まず、VSYNC信号に同期して画面指示を切り替えた場合、書き込みホストからの書き込み先選択の変化と、変化時点での実際の書き込み先が一致しない瞬間があることに気づき、74HC74を撤去しています。

もちろん、実際の書き込み先をホストにフィードバックし、ホストによる選択と一致してから書き込みを開始すれば、その問題は解決するのですが、ホストのリード待ちによる遅延を考慮し、非同期での書き込みおよび書き込み/表示VRAMの切り替えとしました。

後述しますが、表示期間中のVRAM切換による画面乱れは実験範囲内では知覚できませんでした。

また、74HC74に依存していた~#0/#1信号は、VRAMボードが1枚の際には使用されないこと、2枚の際には#0/~#1の反転が信号が~#0_OE信号であることから、~#0_OEを~#0/#1として使用しています。

SW1がSync.かつ、SW2がSingleの際には、変更前の回路と回路上は変更ありません。

SW2がDualの際には垂直ブランキング期間に関係なく、ホストからの#0/~#1信号によってVRAMに対する出力許可信号(~#0_OE or ~#1_OE)が決まるようになっています。書き込み許可信号(~#0_WE or ~#1_WE)についても同様です。

また、SW1がAsync.の際には、~VBLANK信号が入力されていた部分はプルダウン抵抗(回路変更前はプルアップになっていたため、プルダウンに変更)によりLレベルとなり、ホストは常に~VBLANK信号がアクティブとなっているように認識され、またU6の74HC02は単純なNOTゲートとして働きます。

なお、本来は、74HC02の3番ピン、6番ピンにもプルダウン抵抗を用いる必要があるのですが、今回はとりあえず動いてしまったので、すべての端子のプルダウン抵抗を1つにまとめたままにしています。真似してはいけません(^^;;;;;

VRAMボードが1枚の際には、SW1をSync., SW2をSingleに選択することで、垂直ブランキング期間のみに書き込むようになります。この際、ホストは#0/~#1信号をLにしておくことが必要です。

VRAMボードが2枚の際には、SW1をAsync., SW2をDualに選択することで、垂直ブランキング期間に関係なく、ホストで選択されたVRAMを表示し続け、書き込みはホストで選択されていないVRAMに対して行われます(暗黙の書き込み先選択)。

なお、SW1とSW2はSync./SingleかAsync./Dualの組み合わせでしか使用しないため、双極双投のスイッチを使用してもよいのですが、手持ちがなく、単極双投のスイッチを2つ使用しました。

(追記終)

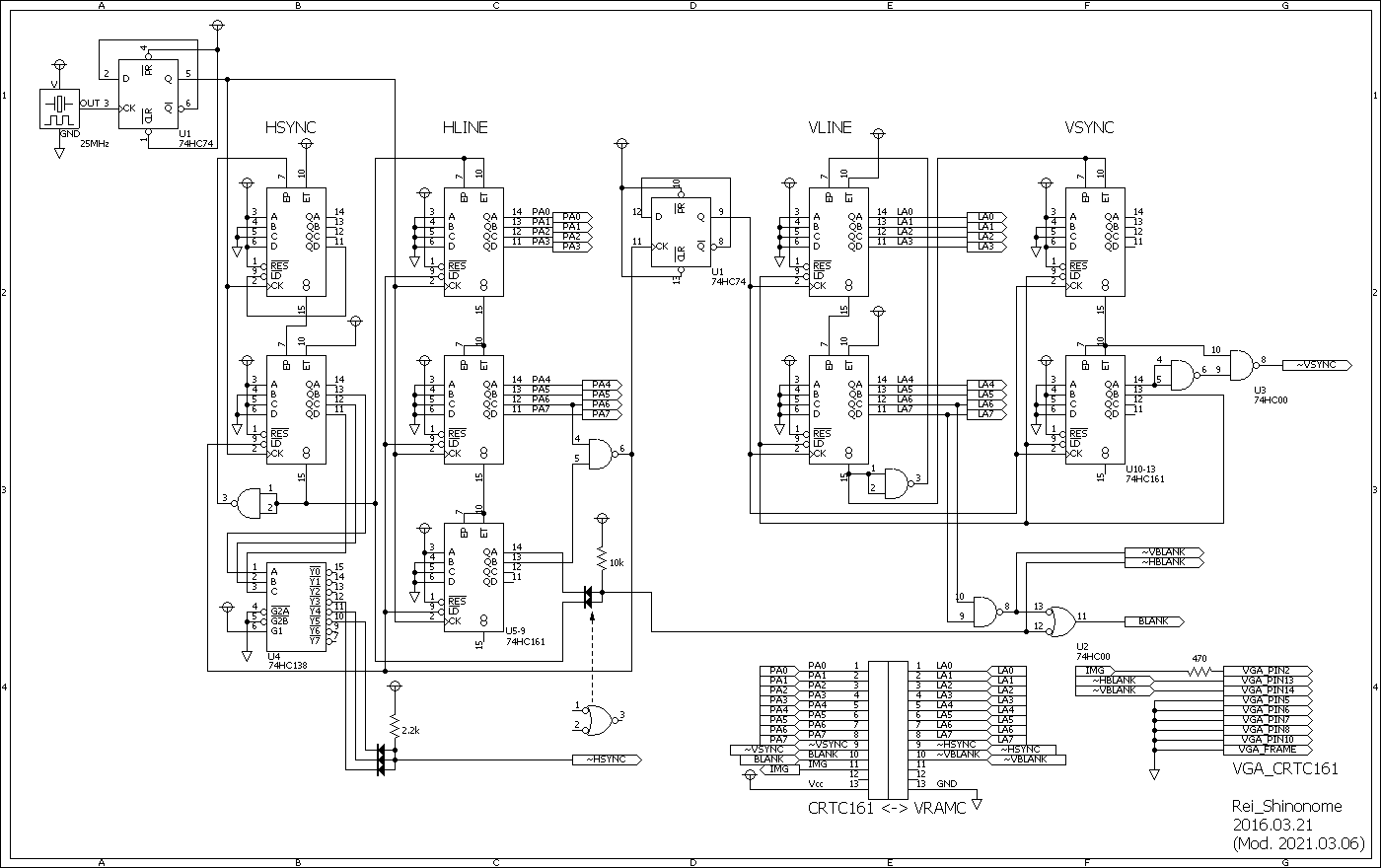

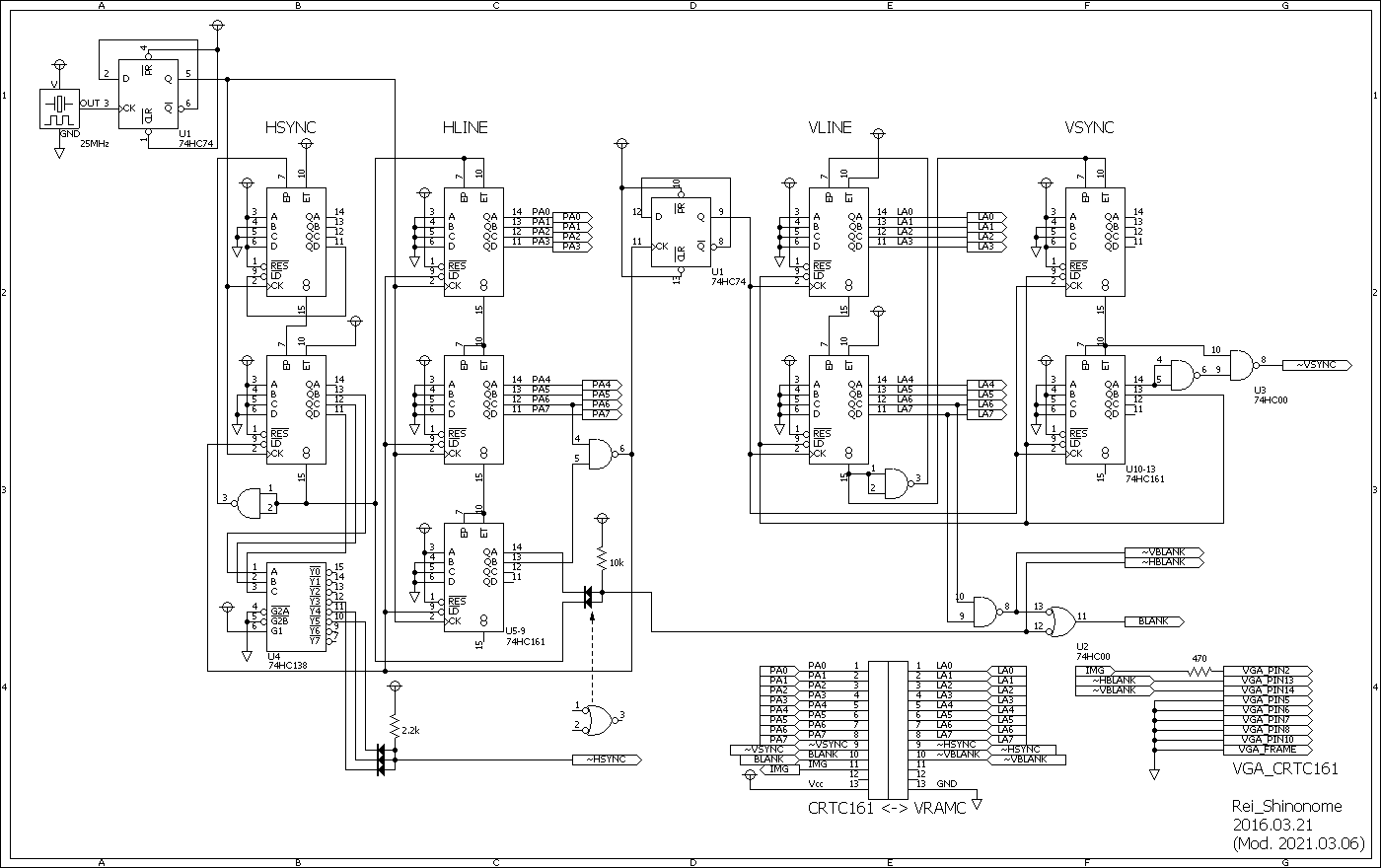

最後に、改造したVGA信号生成回路の回路図です。

VRAMコントローラへの接続端子と、ディスプレイ接続のためのミニD-Sub15ピンコネクタの設置を行いました。

VGAでは、映像入力信号は、インピーダンス75Ωで0.7Vp-pが規定されているため、

0.7[V]/75[Ω] = 9.3[mA]が、5.0[V] - 0.7[V] = 4.3[V]の電圧に対して流れるように、4.3[V]/9.3[mA] ≒ 470Ωの抵抗を挟んで、VRAMボードの74HC153からの出力信号を与えています。

まずは、VRAMボード(2021/03/25追記 マスターVRAM(フレームバッファ)ボード)の回路図です。

VRAMは、垂直方向に4ピクセル分(640x480のスクリーン上では8ピクセル分)を1つのRAMアドレスに格納しています。下位4bitのみ使用していて、上位4bitは使用していません。

RAM領域がもったいないですが、後述するようにホストからのデータ転送に使用するポートが少ないためこのようになってしまいました。

VGA信号生成回路からの画面表示用のVRAMアドレスと、VRAMコントローラからの書き込み用のVRAMアドレスを74HC157で切り替えています。

SRAMのデータバスは、画面表示時と書き込み時で入出力の方向が変わるため、74HC244を用いて方向の制御をしています。

前述の通り4ピクセル分が1つのアドレス内に格納されているため、74HC153に垂直アドレス(ラインアドレス)の下位2bitのアドレスを与えて、各ラインのピクセルデータを分離しています。

74HC153から出力される各水平・垂直方向のアドレスに対応するデータは、VRAMコントローラを経由してVGA信号生成回路まで戻り、その基板からミニD-Subコネクタを通してディスプレイに与えられます。

(2021/03/25 追記)

スレーブVRAM(フレームバッファ)ボードの回路図です。

マスターVRAMボードとの違いは、74HC153の有無、OE/WE端子の配置、LA0/LA1端子の有無のみです。

スレーブVRAMボードから出力されたVRAMデータはC0-3端子を通してマスターVRAMボードの74HC153に送られます。マルチプレクサの節約策です。

トレードオフとして、スレーブVRAMボードは単独で画像を出力することはできなくなっています。

(追記終)

次に、VRAMコントローラ(2021/03/25 追記 VRAMコントローラ/インターフェース)の回路図です。

書き込みアドレスは74HC161を使って、書き込みホスト(FT245R or Arduino)からのクロックで0番地からシーケンシャルに生成します。

FT245Rには汎用ポートが8bitしかないため、コントロールにつかう端子を考えると、8bitのデータを一気に転送することは不可能です。

シフトレジスタを使うことで、クロックとデータの2bitで任意の長さのデータを転送することはできますが、その分オーバーヘッドが生じます。

この点を考慮して、RAMの各番地の8bitの領域をすべて使うことをせず、半分の4bitを使うこととしました。74HC74をシフトレジスタとして使用して、2bitずつ送信します。

VRAMへの書き込みは、垂直ブランキング期間のみ行うため、書き込みホストへは1bitの入力端子を必要とします。

もし、垂直ブランキング期間以外で書き込むと、/WRが/OEに優先されるために、書き込みタイミングでデータバスが奪われ、画面が乱れる原因となります。

表示用アドレスと書き込みアドレスおよびデータはそのまま40pinのコネクタでVRAMに送られます。電源や出力・書き込み信号は別の10pinのコネクタで接続しています。

また、この回路図を見て分かるとおり、VRAMは2段積みが可能な回路になっています。

つまり、片方のVRAM(表示VRAM)の内容の表示中に、もう一方のVRAM(編集VRAM)を書き換えて、表示VRAMと編集VRAMを交代させることができます。

こうすることで、垂直ブランキング期間に関係なくVRAMの内容を書き換えることができ、高速な画面書き換えが可能になります。

そのために、表示VRAMと編集VRAMを指示する信号(回路図中の#0/~#1)も書き込みホストから与えます。

VRAMボード1枚と2枚いずれにも対応できるよう、ここはスイッチで切り替えられるように予定します。

また、40pinコネクタ内のC0-3は、VRAMボード間のデータ出力の通信線です。VRAMボード2段積みの際に、どちらかの一方のVRAMボードの74HC244の出力を選択し、C0-3の通信線に乗せ、74HC153の入力に与えます。

(2021/03/25 追記 上記打消線も含む)

回路変更が生じています。

まず、VSYNC信号に同期して画面指示を切り替えた場合、書き込みホストからの書き込み先選択の変化と、変化時点での実際の書き込み先が一致しない瞬間があることに気づき、74HC74を撤去しています。

もちろん、実際の書き込み先をホストにフィードバックし、ホストによる選択と一致してから書き込みを開始すれば、その問題は解決するのですが、ホストのリード待ちによる遅延を考慮し、非同期での書き込みおよび書き込み/表示VRAMの切り替えとしました。

後述しますが、表示期間中のVRAM切換による画面乱れは実験範囲内では知覚できませんでした。

また、74HC74に依存していた~#0/#1信号は、VRAMボードが1枚の際には使用されないこと、2枚の際には#0/~#1の反転が信号が~#0_OE信号であることから、~#0_OEを~#0/#1として使用しています。

SW1がSync.かつ、SW2がSingleの際には、変更前の回路と回路上は変更ありません。

SW2がDualの際には垂直ブランキング期間に関係なく、ホストからの#0/~#1信号によってVRAMに対する出力許可信号(~#0_OE or ~#1_OE)が決まるようになっています。書き込み許可信号(~#0_WE or ~#1_WE)についても同様です。

また、SW1がAsync.の際には、~VBLANK信号が入力されていた部分はプルダウン抵抗(回路変更前はプルアップになっていたため、プルダウンに変更)によりLレベルとなり、ホストは常に~VBLANK信号がアクティブとなっているように認識され、またU6の74HC02は単純なNOTゲートとして働きます。

なお、本来は、74HC02の3番ピン、6番ピンにもプルダウン抵抗を用いる必要があるのですが、今回はとりあえず動いてしまったので、すべての端子のプルダウン抵抗を1つにまとめたままにしています。真似してはいけません(^^;;;;;

VRAMボードが1枚の際には、SW1をSync., SW2をSingleに選択することで、垂直ブランキング期間のみに書き込むようになります。この際、ホストは#0/~#1信号をLにしておくことが必要です。

VRAMボードが2枚の際には、SW1をAsync., SW2をDualに選択することで、垂直ブランキング期間に関係なく、ホストで選択されたVRAMを表示し続け、書き込みはホストで選択されていないVRAMに対して行われます(暗黙の書き込み先選択)。

なお、SW1とSW2はSync./SingleかAsync./Dualの組み合わせでしか使用しないため、双極双投のスイッチを使用してもよいのですが、手持ちがなく、単極双投のスイッチを2つ使用しました。

(追記終)

最後に、改造したVGA信号生成回路の回路図です。

VRAMコントローラへの接続端子と、ディスプレイ接続のためのミニD-Sub15ピンコネクタの設置を行いました。

VGAでは、映像入力信号は、インピーダンス75Ωで0.7Vp-pが規定されているため、

0.7[V]/75[Ω] = 9.3[mA]が、5.0[V] - 0.7[V] = 4.3[V]の電圧に対して流れるように、4.3[V]/9.3[mA] ≒ 470Ωの抵抗を挟んで、VRAMボードの74HC153からの出力信号を与えています。

4. 製作

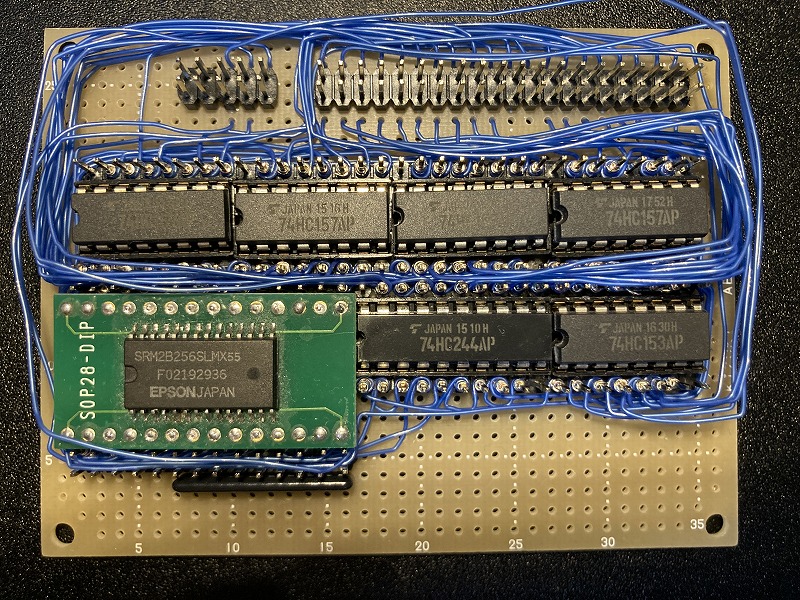

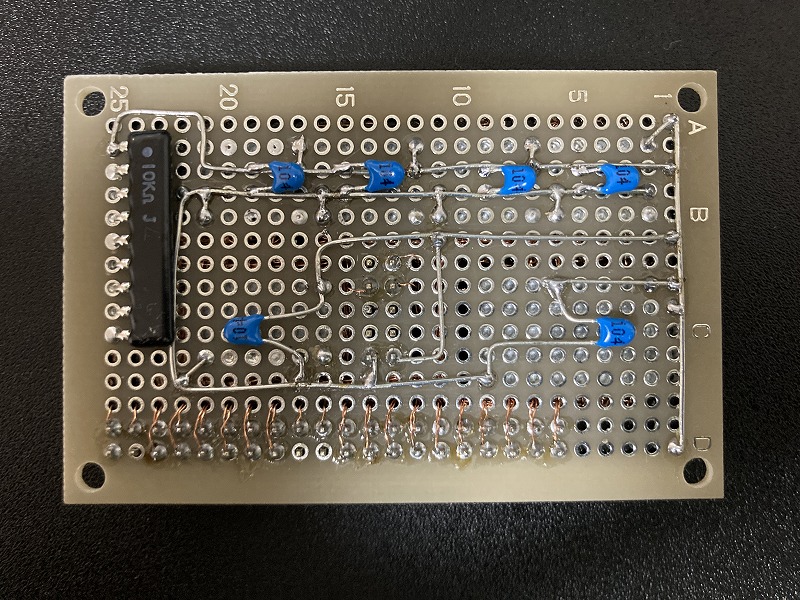

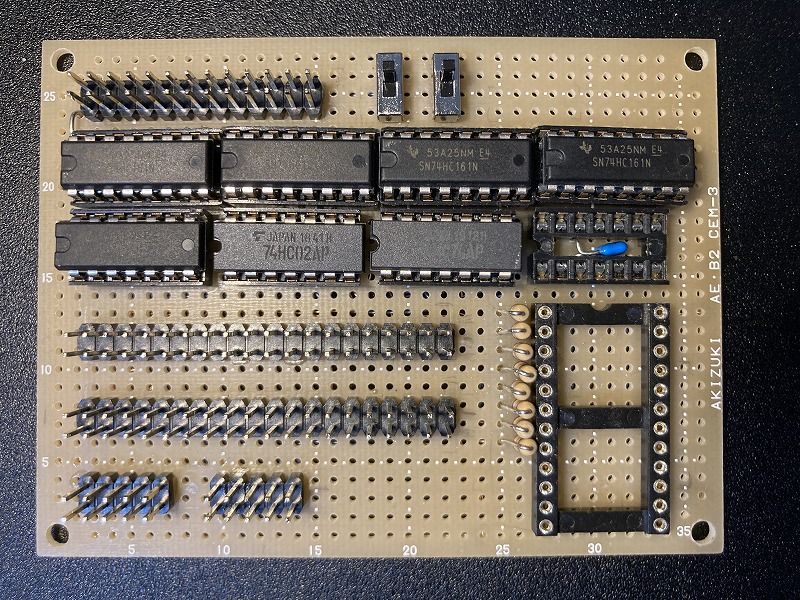

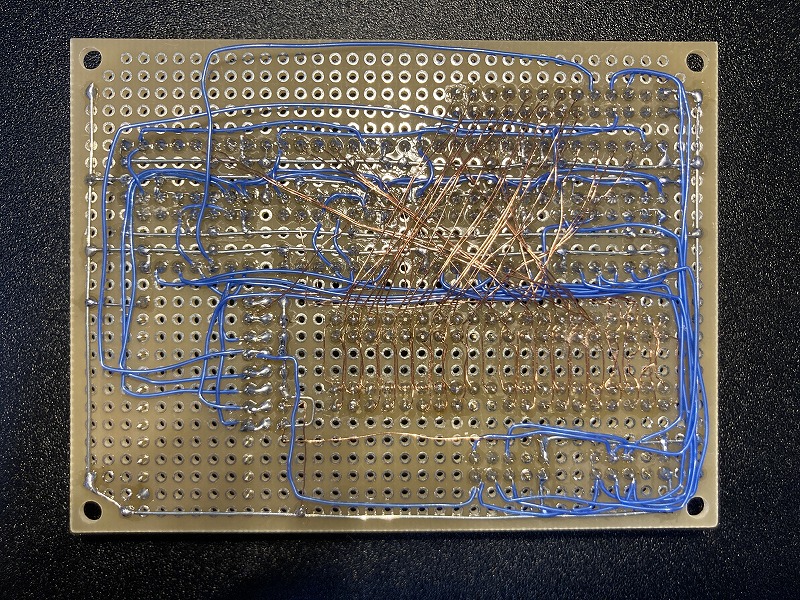

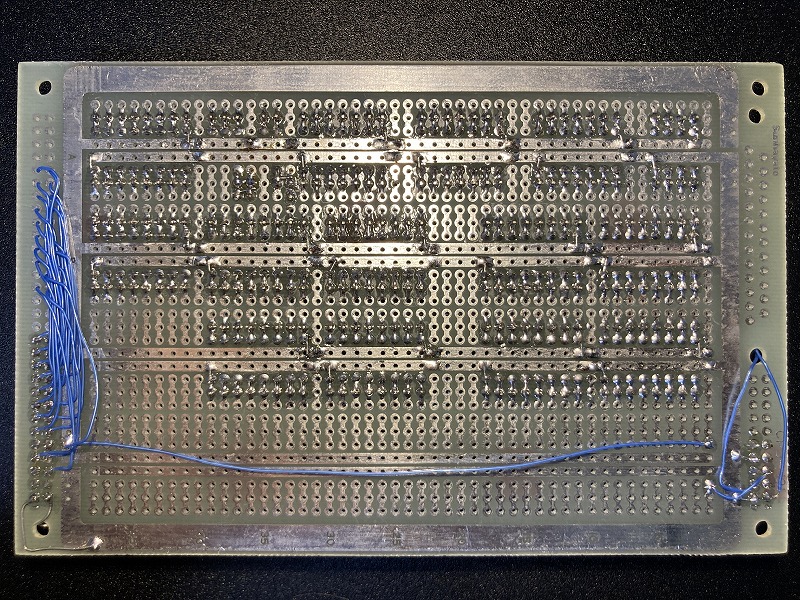

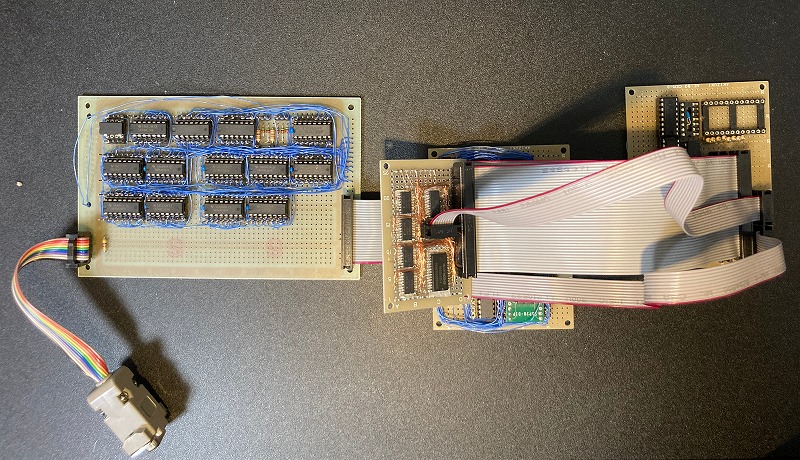

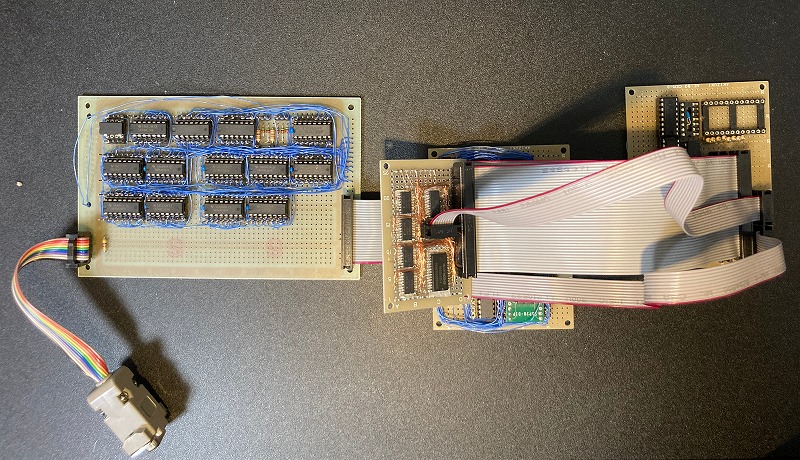

VGA信号生成回路はICパターン基板を使用しましたが、今回は通常のユニバーサル基板で製作しています。

大量のICを詰め込むため、過密実装です。

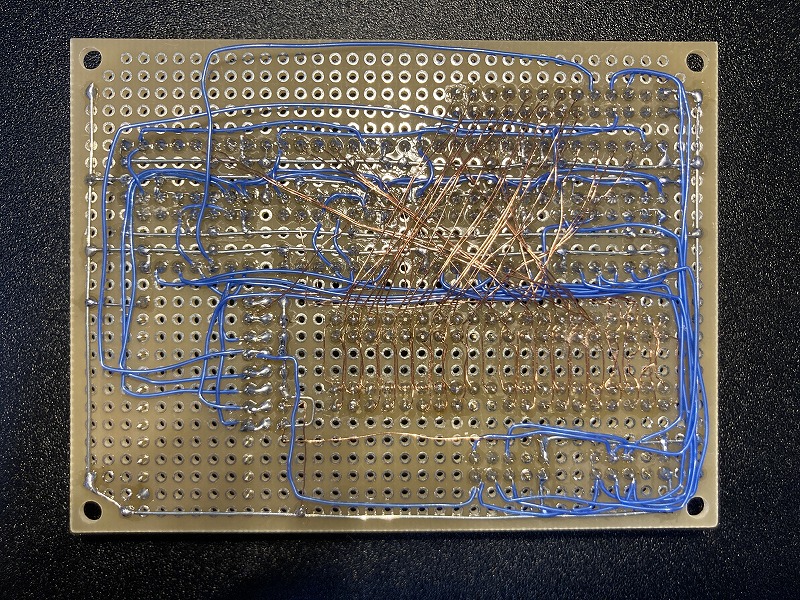

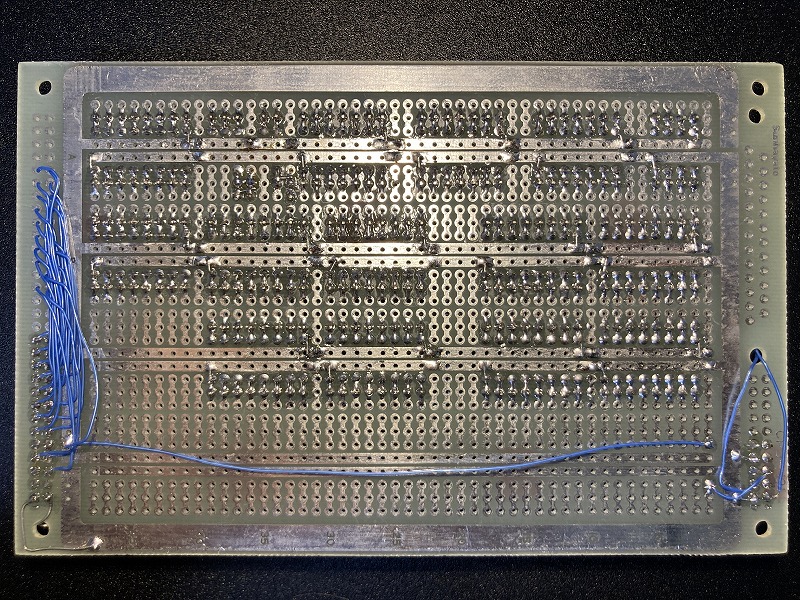

VRAMボード(2021/03/25追記 マスターVRAMボード)は、VGA信号生成回路と同様にラッピングポスト代わりのピンヘッダを用いてワイヤラッピングで製作しました。

最初に0.6mm径のスズメッキ線で電源ラインを配線し、ICを実装する場所の直下にパスコンをハンダ付けします。その上からICソケットを実装し、パスコンを埋めてしまいます。

(パスコン埋め)

ICソケットの両脇にはラッピングポスト代わりのピンヘッダをハンダ付けし、ピンヘッダとICソケットを部品の足で短絡するようにハンダ付けします。

これでワイヤラッピングによる配線の準備ができたので、ワイヤラッピングで順次配線していきます。基板の外側から配線していかないと、配線済みのETFE線の厚さで、十分な深さにラッピングワイヤを巻き付けられなくなってしまいます。

データバスのプルアップ抵抗と、VRAMコントローラとの接続に使うピンヘッダのみ、ハンダ面で配線しています。

(左:表面 超・盛りソバ(_ _;;; 右:裏面 集合抵抗とデータバス間のみ配線されていてすっきり)

(2021/03/25 追記)

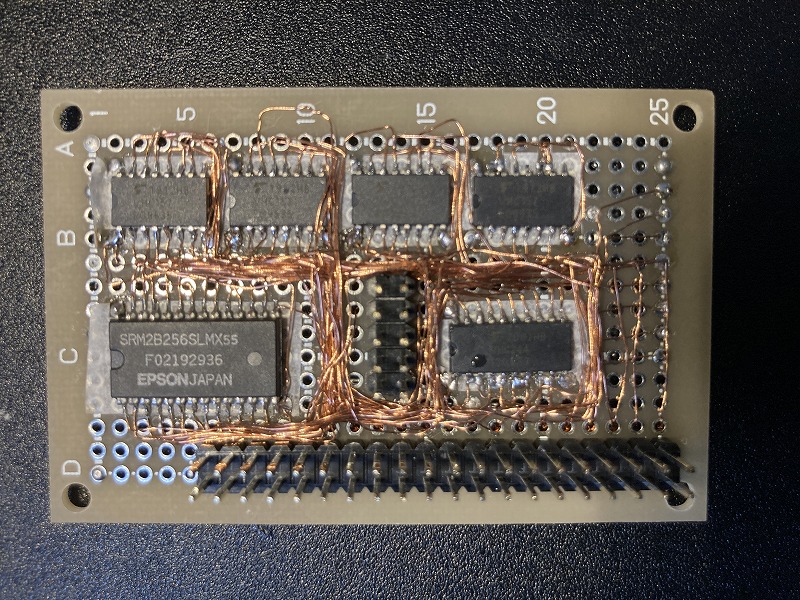

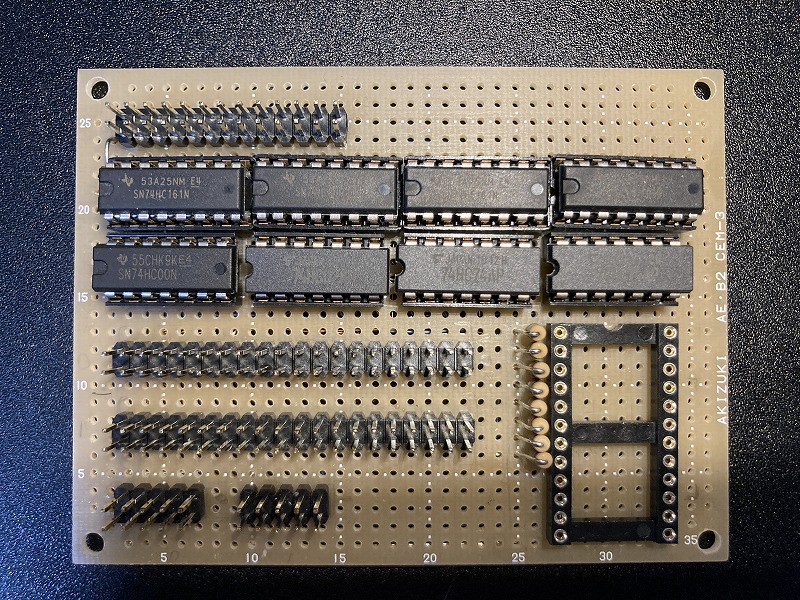

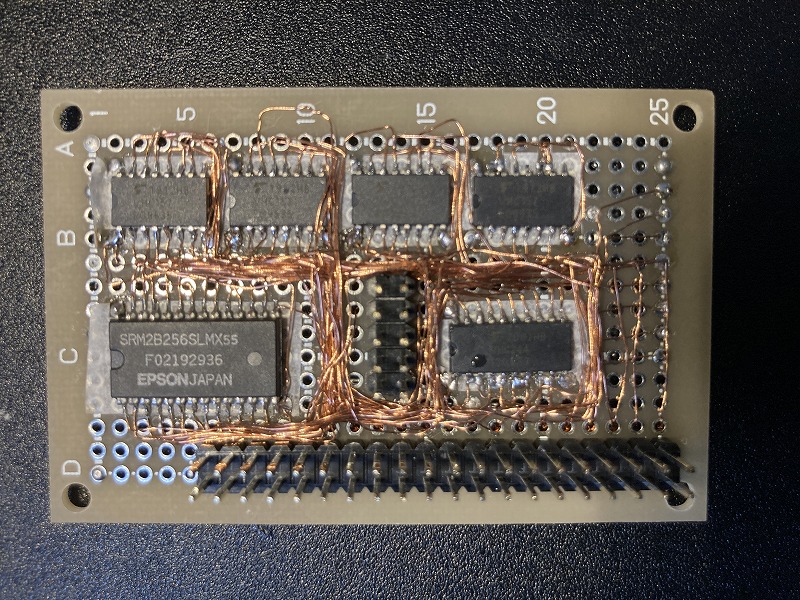

スレーブVRAMボードも製作しました。DIPの74シリーズICが集まりにくくなっているため、思い切って、すべてSOP品で製作しました。

74VHC157と74VHC244を使用していますが、速度の問題ではなく、入手しやすかったからという理由です。入手可能であればそれぞれHCで構いません。

表面実装なので、裏側に配線した電源ラインを容易に表に接続できるよう、スルーホール基板を使用しています。また、74VHC244の隣接端子の接続にも役立っています。

一方で、スルーホールのランドを通して裏表および隣接ピンがショートしないように、クッキングシートを小さく切って、各ICが配置される基板上の位置に貼り付け、ランドが必要な部分のみ切り欠いています。

(これらの配線・実装の方法はChaN氏のサイトの記述を大いに参考にしています。)

ピンヘッダは隙間に配置しました。

(左:表面 UEWが飛び交います 74VHC244上の液体は固着したフラックスです(^^; 右:裏面 集合抵抗とパスコンは裏面に配置しました。本来はこれも面実装部品を使うべきでしょうが・・・)

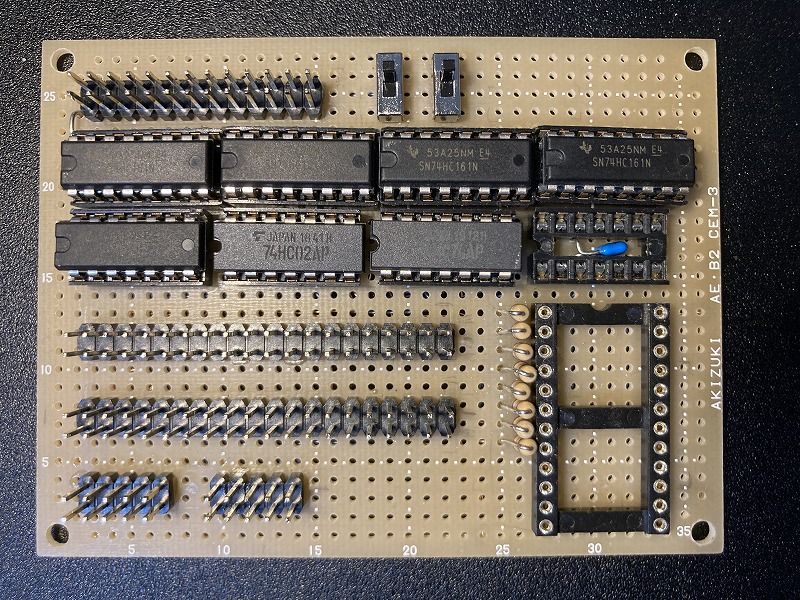

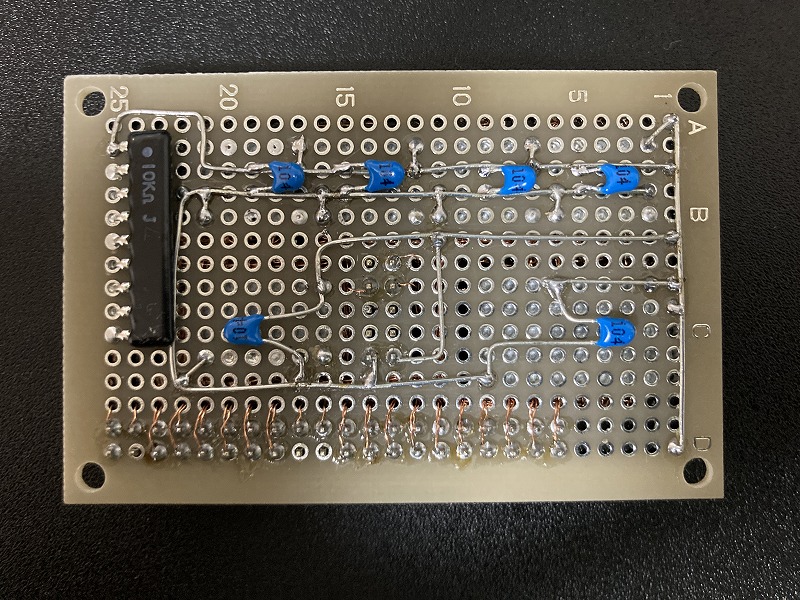

VRAMコントローラは大量のICに加え、AE-FT245Rや基板間接続のピンヘッダが存在し、ラッピングポスト代わりのピンヘッダのスペースを取れなかったため、ハンダ面での配線を行いました。

電源ラインとパスコン埋めまでは同じです。AWG30のETFE線で、バス配線以外のコントロール配線を行い、その後、0.2mm径のUEW線でバス配線を行いました。

UEW線は、ハンダゴテにハンダを少量盛って、被服を剥がしたいところをハンダで温めると、被覆除去と予備ハンダが同時に行えるため、バス配線に向いています。

(左:表面 VRAMボードと違ってスッキリしています 右:UEWが細いのでバス配線をしても盛りソバになりません)

(2021/03/25追記 中央:回路変更後の基板 スイッチが追加され、74HC74が撤去されています。)

VGA信号生成回路に使用したサンハヤトのICパターン基板CPU-131は、基板の両端にピンヘッダを立ててくださいと言わんばかりに2列2.54mmピッチの穴が開いているため、ここにピンヘッダを実装しました。

1つは10pinで、IDCリボンケーブルを半分に切ったものにミニD-Sub15ピンコネクタをハンダ付けし、基板からミニD-Sub15ピンコネクタを引き出せるようにしました。

もう1つは26pinで、表示ピクセル・ラインのアドレスと同期信号やブランク信号、電源をVRAMコントローラに送っています。

また、今回の製作に先立った予備実験中に、HSYNC信号の鈍りが見られたため、5年前の回路からHSYNCのAND(負論理OR)回路の抵抗を2.2kΩに換装しています(上記回路図参照)。

(左:表面 ピンヘッダが増設されました 右:裏面 ピンヘッダへの配線と、VRAMからのデータをD-Sub15ピンコネクタへ送るための配線はハンダ面で行いました)

大量のICを詰め込むため、過密実装です。

VRAMボード(2021/03/25追記 マスターVRAMボード)は、VGA信号生成回路と同様にラッピングポスト代わりのピンヘッダを用いてワイヤラッピングで製作しました。

最初に0.6mm径のスズメッキ線で電源ラインを配線し、ICを実装する場所の直下にパスコンをハンダ付けします。その上からICソケットを実装し、パスコンを埋めてしまいます。

(パスコン埋め)

ICソケットの両脇にはラッピングポスト代わりのピンヘッダをハンダ付けし、ピンヘッダとICソケットを部品の足で短絡するようにハンダ付けします。

これでワイヤラッピングによる配線の準備ができたので、ワイヤラッピングで順次配線していきます。基板の外側から配線していかないと、配線済みのETFE線の厚さで、十分な深さにラッピングワイヤを巻き付けられなくなってしまいます。

データバスのプルアップ抵抗と、VRAMコントローラとの接続に使うピンヘッダのみ、ハンダ面で配線しています。

(左:表面 超・盛りソバ(_ _;;; 右:裏面 集合抵抗とデータバス間のみ配線されていてすっきり)

(2021/03/25 追記)

スレーブVRAMボードも製作しました。DIPの74シリーズICが集まりにくくなっているため、思い切って、すべてSOP品で製作しました。

74VHC157と74VHC244を使用していますが、速度の問題ではなく、入手しやすかったからという理由です。入手可能であればそれぞれHCで構いません。

表面実装なので、裏側に配線した電源ラインを容易に表に接続できるよう、スルーホール基板を使用しています。また、74VHC244の隣接端子の接続にも役立っています。

一方で、スルーホールのランドを通して裏表および隣接ピンがショートしないように、クッキングシートを小さく切って、各ICが配置される基板上の位置に貼り付け、ランドが必要な部分のみ切り欠いています。

(これらの配線・実装の方法はChaN氏のサイトの記述を大いに参考にしています。)

ピンヘッダは隙間に配置しました。

(左:表面 UEWが飛び交います 74VHC244上の液体は固着したフラックスです(^^; 右:裏面 集合抵抗とパスコンは裏面に配置しました。本来はこれも面実装部品を使うべきでしょうが・・・)

VRAMコントローラは大量のICに加え、AE-FT245Rや基板間接続のピンヘッダが存在し、ラッピングポスト代わりのピンヘッダのスペースを取れなかったため、ハンダ面での配線を行いました。

電源ラインとパスコン埋めまでは同じです。AWG30のETFE線で、バス配線以外のコントロール配線を行い、その後、0.2mm径のUEW線でバス配線を行いました。

UEW線は、ハンダゴテにハンダを少量盛って、被服を剥がしたいところをハンダで温めると、被覆除去と予備ハンダが同時に行えるため、バス配線に向いています。

(左:表面 VRAMボードと違ってスッキリしています 右:UEWが細いのでバス配線をしても盛りソバになりません)

(2021/03/25追記 中央:回路変更後の基板 スイッチが追加され、74HC74が撤去されています。)

VGA信号生成回路に使用したサンハヤトのICパターン基板CPU-131は、基板の両端にピンヘッダを立ててくださいと言わんばかりに2列2.54mmピッチの穴が開いているため、ここにピンヘッダを実装しました。

1つは10pinで、IDCリボンケーブルを半分に切ったものにミニD-Sub15ピンコネクタをハンダ付けし、基板からミニD-Sub15ピンコネクタを引き出せるようにしました。

もう1つは26pinで、表示ピクセル・ラインのアドレスと同期信号やブランク信号、電源をVRAMコントローラに送っています。

また、今回の製作に先立った予備実験中に、HSYNC信号の鈍りが見られたため、5年前の回路からHSYNCのAND(負論理OR)回路の抵抗を2.2kΩに換装しています(上記回路図参照)。

(左:表面 ピンヘッダが増設されました 右:裏面 ピンヘッダへの配線と、VRAMからのデータをD-Sub15ピンコネクタへ送るための配線はハンダ面で行いました)

5. 実験

まずは、各基板を3枚の基板をリボンケーブルで接続します。

(装置全景(2021/03/25 追記 下:スレーブVRAMボードを追加した際の装置全景))

...完成時の基板配置を考えずに、各基板に部品を詰め込むことしか考えていなかったので、向きやケーブルの重なりが大変見苦しくなってしまいました(^^;

(2021/03/25 追記)

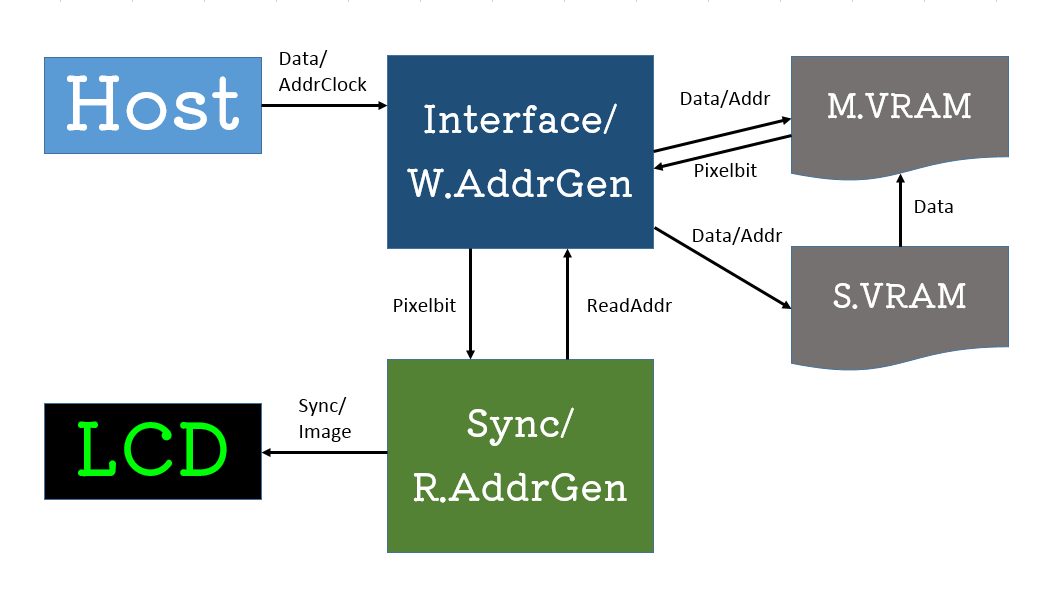

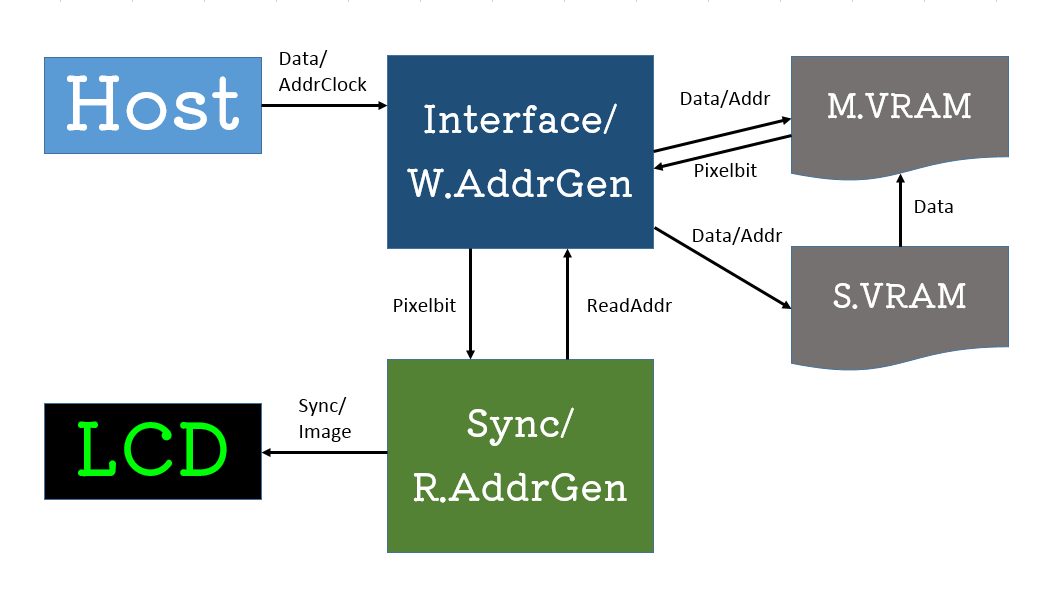

接続ブロック図は次の通りです。

(追記終)

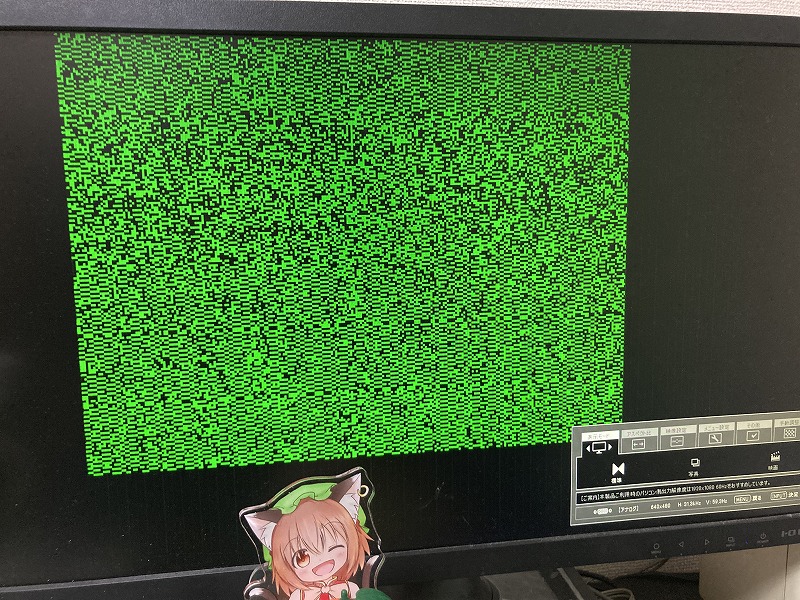

ともかく、動けばよいので、ディスプレイをミニD-Sub15ピンコネクタで接続し、5V電源を供給します。

5年前はacerのV173でしたが、今回はI-O DATAのEX-LD2071TBです。フルHDモニタですが、アナログRGB入力、640x480のVGAにも当然対応しています。

(左:クリックで拡大 右:VGAの640x480 H:31.47kHz V:59.94Hzからは逸脱していても表示可能)

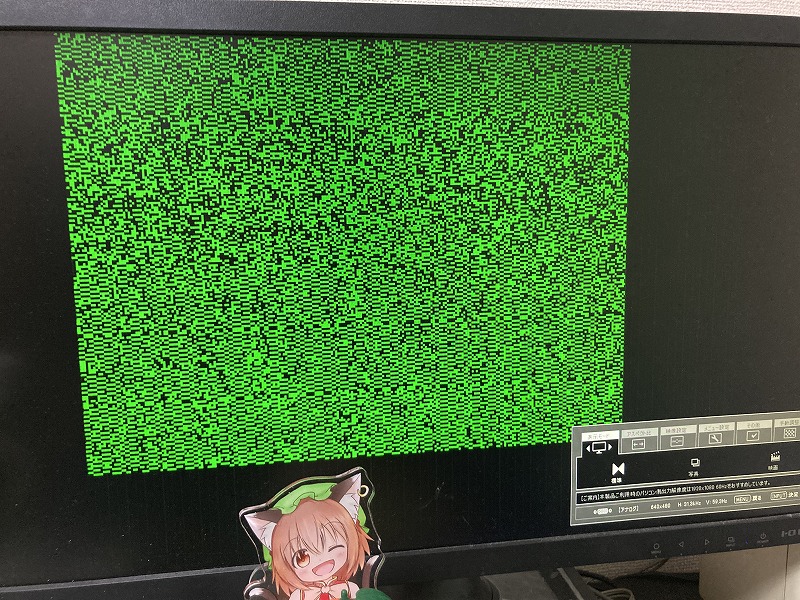

ディスプレイにはランダムなドットパターンが表示されていて、VRAMの内容が表示されていることがわかります(SRAMは電源投入時のデータ内容は不定)。

垂直ブランキング期間以外でVRAMの内容が表示されているため、74HC244も正しく出力を制御できていることがわかります。

各ピクセルもブレなく表示されています。VGA表示タイミングも許容範囲におさまっているようです。

次に、FT245RLを使って、VRAMの内容を書き換えてみます。まずは、ランダムドットパターンをクリアしてみます。

FT245RLに与えるビットパターンは、「書き込みアドレスリセット」の後、「下位2bitのデータ出力」→「下位2bitのデータラッチ」→「上位2bitのデータ出力」→「VRAM書き込み」→「書き込みアドレスインクリメント」の繰り返しです。

「下位2bitのデータ出力」から「VRAM書き込み」の前後で垂直ブランキング期間信号をチェックし、垂直ブランキング期間内に間に合わなかった場合は、書き込みアドレスをそのままにして書き込みをやり直します。

このビットパターンを与えるプログラムを、Visual Studio 2019 CommunityのC++で作成し、実行してみました。

その結果がこれです。

...あまりにも遅すぎます。1フレームの書き換えに90秒近くかかってしまいました。

たしかに、FT245Rで端子入力の読み取りが遅いのは承知していましたが、垂直ブランキング期間のポーリングには耐えきれませんでした。

Synchronous Bit Bangモードも試してみましたが、読み取り前に書き込みを必要とするため、速度改善には貢献しませんでした。

さすがにマズいと思い、「Intel 8254を使用したBeep音再生装置」を「Intel 8254を使用した簡易MIDI音源装置」としたときのように、FT245Rの代わりにArduinoを使用してみました。

ArduinoもC言語でAVRのプログラムを記述できるため、プログラムを流用して、接続・実行してみました。

圧倒的に速いです。約3fpsの速さがあります。

せっかくなので、文字も簡単に表示してみました。

(追記 2021/03/25)

VRAMを2枚にしたことで、垂直ブランキング期間を待たずにVRAMにフレームデータを書き込むことができ、高速な画面書き換えが可能になりました。

この回路において、16MHz動作のATmega328PのmicroSD→SRAMへの転送速度では、10fpsが限界(アセンブラを使用すればもう少し速くなるかもしれませんが)でしたが、その範囲においては上述の74HC74の撤去による、表示期間中のフレームバッファ交代による画面の乱れはほぼ知覚できませんでした。

しかし、10fpsもあれば、動画再生も可能になります。この回路で動画を再生した実験動画も撮影しました。

(装置全景(2021/03/25 追記 下:スレーブVRAMボードを追加した際の装置全景))

...完成時の基板配置を考えずに、各基板に部品を詰め込むことしか考えていなかったので、向きやケーブルの重なりが大変見苦しくなってしまいました(^^;

(2021/03/25 追記)

接続ブロック図は次の通りです。

(追記終)

ともかく、動けばよいので、ディスプレイをミニD-Sub15ピンコネクタで接続し、5V電源を供給します。

5年前はacerのV173でしたが、今回はI-O DATAのEX-LD2071TBです。フルHDモニタですが、アナログRGB入力、640x480のVGAにも当然対応しています。

(左:クリックで拡大 右:VGAの640x480 H:31.47kHz V:59.94Hzからは逸脱していても表示可能)

ディスプレイにはランダムなドットパターンが表示されていて、VRAMの内容が表示されていることがわかります(SRAMは電源投入時のデータ内容は不定)。

垂直ブランキング期間以外でVRAMの内容が表示されているため、74HC244も正しく出力を制御できていることがわかります。

各ピクセルもブレなく表示されています。VGA表示タイミングも許容範囲におさまっているようです。

次に、FT245RLを使って、VRAMの内容を書き換えてみます。まずは、ランダムドットパターンをクリアしてみます。

FT245RLに与えるビットパターンは、「書き込みアドレスリセット」の後、「下位2bitのデータ出力」→「下位2bitのデータラッチ」→「上位2bitのデータ出力」→「VRAM書き込み」→「書き込みアドレスインクリメント」の繰り返しです。

「下位2bitのデータ出力」から「VRAM書き込み」の前後で垂直ブランキング期間信号をチェックし、垂直ブランキング期間内に間に合わなかった場合は、書き込みアドレスをそのままにして書き込みをやり直します。

このビットパターンを与えるプログラムを、Visual Studio 2019 CommunityのC++で作成し、実行してみました。

その結果がこれです。

USB経由でVRAMの書き換えができてる!!!

— 東雲玲β@Ugo (@Rei_S_Ugo) 2021年2月27日

が、VBLANK期間を待っているのでクソ遅い!!! pic.twitter.com/mRk15E0FZt

...あまりにも遅すぎます。1フレームの書き換えに90秒近くかかってしまいました。

たしかに、FT245Rで端子入力の読み取りが遅いのは承知していましたが、垂直ブランキング期間のポーリングには耐えきれませんでした。

Synchronous Bit Bangモードも試してみましたが、読み取り前に書き込みを必要とするため、速度改善には貢献しませんでした。

さすがにマズいと思い、「Intel 8254を使用したBeep音再生装置」を「Intel 8254を使用した簡易MIDI音源装置」としたときのように、FT245Rの代わりにArduinoを使用してみました。

ArduinoもC言語でAVRのプログラムを記述できるため、プログラムを流用して、接続・実行してみました。

おなじプログラムをArduinoUNOに移植したら一瞬で書き換えてくれて草生えてる

— 東雲玲β@Ugo (@Rei_S_Ugo) 2021年3月1日

FT245遅すぎる pic.twitter.com/IQvKMi9wQT

圧倒的に速いです。約3fpsの速さがあります。

せっかくなので、文字も簡単に表示してみました。

画面ごとに2秒のウエイト入れるプログラムにしてもこの速さ

— 東雲玲β@Ugo (@Rei_S_Ugo) 2021年3月1日

やっぱマイクロコントローラって偉大だわ pic.twitter.com/rRvGcAHdhs

(追記 2021/03/25)

VRAMを2枚にしたことで、垂直ブランキング期間を待たずにVRAMにフレームデータを書き込むことができ、高速な画面書き換えが可能になりました。

この回路において、16MHz動作のATmega328PのmicroSD→SRAMへの転送速度では、10fpsが限界(アセンブラを使用すればもう少し速くなるかもしれませんが)でしたが、その範囲においては上述の74HC74の撤去による、表示期間中のフレームバッファ交代による画面の乱れはほぼ知覚できませんでした。

しかし、10fpsもあれば、動画再生も可能になります。この回路で動画を再生した実験動画も撮影しました。

6. あとがき

5年の歳月を経て、VGA信号生成回路を本来の意図で動かすことができました。

バス調停回路に同じマルチプレクサを、アドレス生成部にカウンタをそれぞれ4つ使用するため、今となっては貴重なDIPのロジックICを消費してしまい、ちょっともったいない気持ちになりながら製作しました。

この制作中に、VGA信号生成回路の発振器(25MHz)の仕様を勘違いしていたことに気づきました。

この発振器はDIP8ピンで、1番ピンが発振出力を制御するピンですが、NCだと勘違いして、5年間、オープンのままにしていました(_ _;;

今回の実験中に、発振が止まったり、また発振したりを繰り返していたため、発振器が故障したのかと思い、データシートを参照したところ発覚しました。

1番ピンをVccに接続し、部屋を常温まで温めたところ、安定して発振するようになりました。

任意の画像を表示しようとすると、FT245R経由でPCから直接画像データを送るのは、速度面で非現実的であるため、マイクロコントローラとSDカードを使用した回路を検討する必要があるでしょう。

この回路自体は、VRAMへの書き込み時のバス調停回路があるため、Arduinoに限らず、任意のマイコンを接続することができます。VRAMコントローラの74HC74をバイパスすれば、4bitを一気に転送することもできます。

また、書き込みアドレスを生成する74HC161は任意の値のロードも可能なため、アドレスを与えるレジスタを用意すれば、VRAMへのランダムアクセス書き込みも可能になるでしょう。

このあたりは、VRAMのホストとなる機器に合わせて柔軟に改造する余地があります。

バス調停回路に同じマルチプレクサを、アドレス生成部にカウンタをそれぞれ4つ使用するため、今となっては貴重なDIPのロジックICを消費してしまい、ちょっともったいない気持ちになりながら製作しました。

この制作中に、VGA信号生成回路の発振器(25MHz)の仕様を勘違いしていたことに気づきました。

この発振器はDIP8ピンで、1番ピンが発振出力を制御するピンですが、NCだと勘違いして、5年間、オープンのままにしていました(_ _;;

今回の実験中に、発振が止まったり、また発振したりを繰り返していたため、発振器が故障したのかと思い、データシートを参照したところ発覚しました。

1番ピンをVccに接続し、部屋を常温まで温めたところ、安定して発振するようになりました。

任意の画像を表示しようとすると、FT245R経由でPCから直接画像データを送るのは、速度面で非現実的であるため、マイクロコントローラとSDカードを使用した回路を検討する必要があるでしょう。

この回路自体は、VRAMへの書き込み時のバス調停回路があるため、Arduinoに限らず、任意のマイコンを接続することができます。VRAMコントローラの74HC74をバイパスすれば、4bitを一気に転送することもできます。

また、書き込みアドレスを生成する74HC161は任意の値のロードも可能なため、アドレスを与えるレジスタを用意すれば、VRAMへのランダムアクセス書き込みも可能になるでしょう。

このあたりは、VRAMのホストとなる機器に合わせて柔軟に改造する余地があります。

7. 参考にさせていただいたサイト・情報

- コンピュータを作ろう

- Microcontroller VGA Interface projects

- Martin Hinner's homepage

- ELM by ChaN(2021/03/25 追記)

上へ

戻る