2023/02/11 アクセスカウンタ・アクセス解析タグ入れ替え(内容に変更ありません)

2016/01/30 解析タグ追加(内容に変更ありません)

目次

1. 概要2. 回路図

3. 実装

4. あとがき

5. 参考にさせていただいたサイト・情報

1. 概要

汎用ロジックICである74シリーズのLSタイプはDTL(Diode Transistor Logic)で構成されています。

そのなかの74LS74はD-Type Flip-Flopで、3入力NANDゲート6つで構成されています。

そこで、NANDゲートの内部回路を省略した回路を汎用のダイオードとトランジスタを使って構成し、それを6つつなぐことでD-FFを製作しました。

2. 回路図

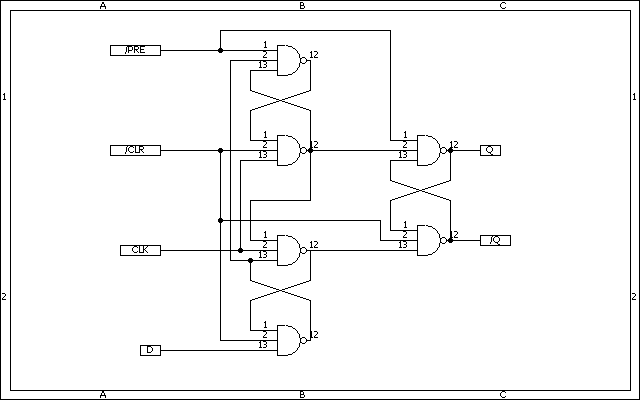

まずは、NANDゲートを用いたD-FFの回路図です。

「Logisim上で作る全NANDTD4」で示したものと同じです。

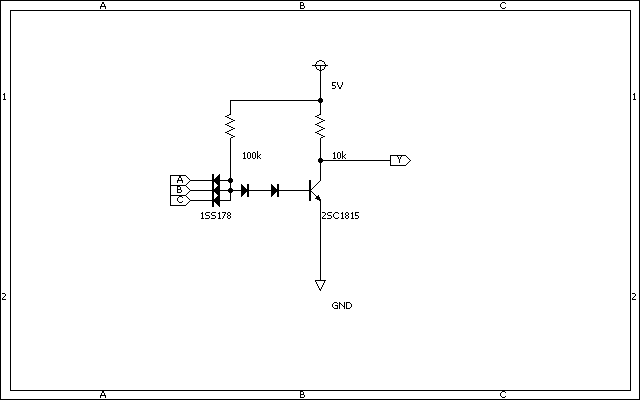

この各NANDゲートは次のようなDTL回路として構成されています。

非常に簡単かつ、何も考えていない回路です。(^^;

入力がLの時は1入力当たり(5-0.6)/100k=44uAだと思われます。電流計を持っていないので測定していません。

DTLは、入力がどれか1つでもLになると、順方向電圧の低い入力側に電流がながれ、トランジスタがオフとなり、出力に対して抵抗を介してHレベルの電圧がかかります。

一方、全てHであると、トランジスタのB-E間に電流がながれ、トランジスタがオンとなり、C-E間に電流が流れるため、出力はLとなります。

3. 実装

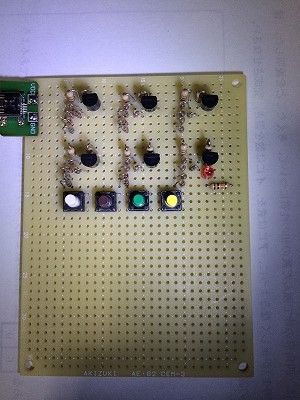

電源は簡単に5Vを取れるUSBインターフェイスからとりました。

1ゲートあたりの面積を小さくするためダイオード・抵抗は立てています。

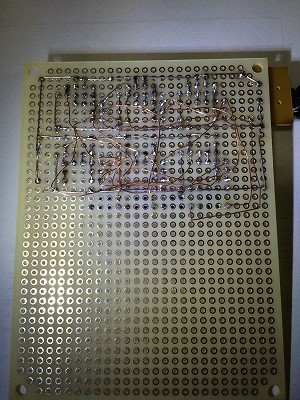

各素子はすべて抵抗・ダイオードの足で配線し、素子間はUEWで適当に配線しています。

スイッチは各入力とGNDをショートさせるスイッチで、プルアップはしていません。したがって、CLKはスイッチを離した瞬間に入力されます。

LEDは10kΩの抵抗を介してカソードを/Qに接続しています。Qの出力がHになるときに点灯します。

(左:表面 右:裏面 あいかわらずのグチャグチャです)

4. あとがき

部品のフォールディング・はんだ付け・配線を含めて各NAND素子を作るのに約30分かかっています。単純作業なのでほとんど何も考えずに作れました。半田付けは順番を工夫すれば配線の手間が減らせそうでしたがそれを考えつくころには6素子出来上がっていました。

ちゃんとした出力を取るには出力段にバッファ(インバータ)をさらに加える必要があると考えられます。

74LS74の内部回路はQや/Q出力を強制的にVccやGNDに接続してしまうと、D-FFがセット/リセットされてしまうという欠点があります。そのため、バッファ(インバータ)を接続しなければ、出力にヘタに負荷をつなぐと正しく動作しない恐れがあります。

トーテムポール出力を組めば電流も安定して取れると思います。今回は実験なので特にこれらの措置は取りませんでした。

DTLのいいところはゲートの入力をダイオード1本で簡単に増やせるということです。みみっちい話ですが、TTLとして2SC1815を1石追加するよりも、DTLとしてダイオードを1本追加した方が単価が安いのです・・・

5. 参考にさせていただいたサイト・情報

上へ戻る